| 材料圆桌 | 您所在的位置:网站首页 › 芯片制程 nm › 材料圆桌 |

材料圆桌

|

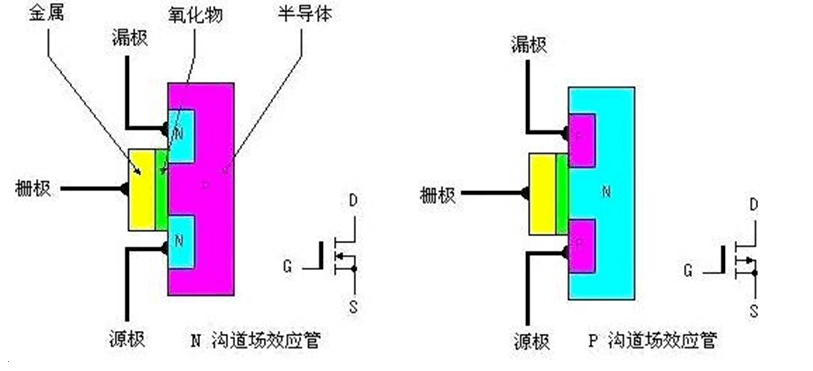

01 芯片工艺制程与晶体管尺寸 芯片中最具代表性的晶体管,称为金属-氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor, MOSFET),它的结构如下:

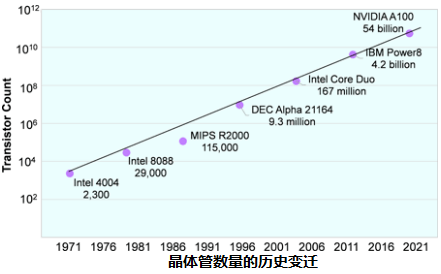

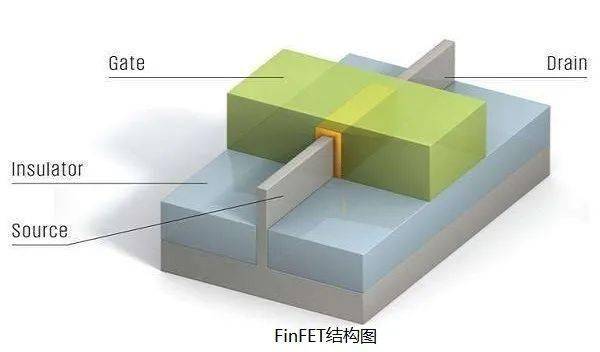

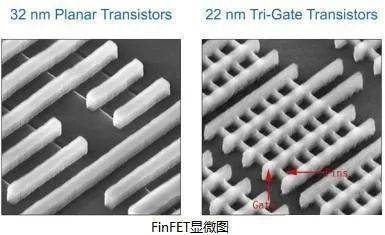

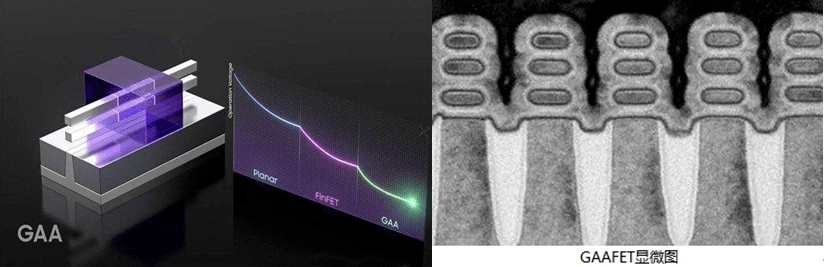

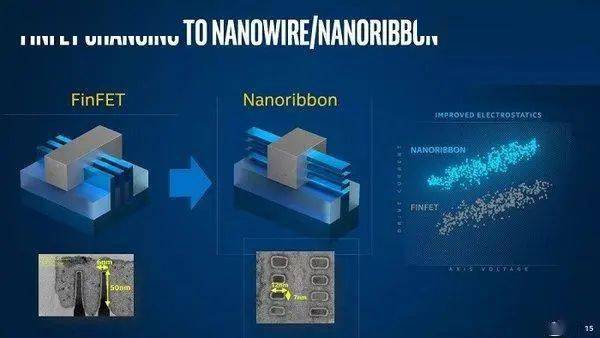

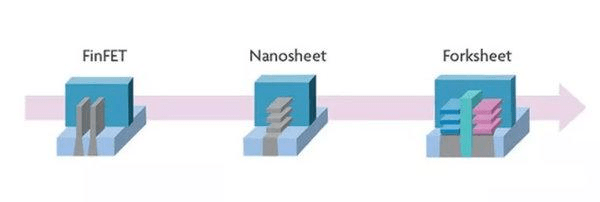

当向源极(Source)与漏极(Drain)间加电压时,电流可以通过沟道从源极流向漏极,而金属栅极(Gate)通过向沟道施加电场影响载流子在沟道中的运动,以控制源漏极间电流的通断,产生“0”“1”信号。 传统意义中, 栅极的最小宽度(Gate Length),或沟道的长度,即为Xnm制程工艺中的数值。微电子技术的发展与进步,主要靠工艺技术的不断改进,使得晶体管尺寸不断缩小,从而集成度不断提高,功耗降低,器件性能得到提高。芯片制造工艺在1995年以后,以当前处理器的制程工艺乘以0.714即可得出下一代CPU的制程工艺,即从一开始的500nm,迭代到如今的14nm、10nm、7nm等。 02 场效应晶体管的新型结构 随着工艺制程推进,场效应晶体管已逐渐脱离原本固定的结构(planar FET)。 美籍华人胡正明教授于2000年发明 FinFET(鳍式场效晶体管,Fin Field-Effect Transistor)。 FinFET的沟道区域是一个被栅极包裹的鳍状半导体。沿源漏方向的鳍的长度,为沟道长度。栅极包裹的结构增强了栅的控制能力,对沟道提供了更好的电学控制。

2021年,三星与台积电相继公布以 GAAFET(全环栅晶体管,Gate all around Field Effect Transistors)结构承载的3nm制程技术。

其通过纳米片(Nanosheet)制造出 MBCFET(多桥通道场效应管),可显著增强晶体管性能,主要取代FinFET晶体管技术。

对于未来晶体管向着更小尺寸的发展,IMEC提出一种创新的架构,称为 ForksheetFET。Forksheet可以理解为是Nanosheet的自然延伸,Forksheet拥有有更紧密的结构,减少面积缩放,与Nanosheet FET相比,在相同制程下的Forksheet FET电路将更加紧凑,具有超出2nm技术节点的额外缩放和性能。

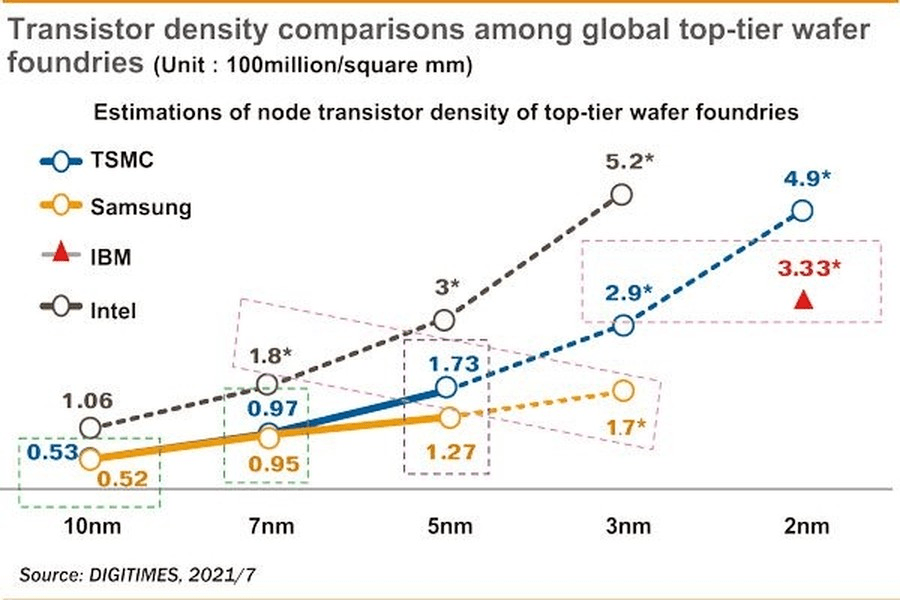

03 芯片制造工艺判断标准的变迁 从以上新型FET结构可以看出, “ 工艺制程=栅极长度”这样工艺制程等同于物理尺寸的说法已然失去意义。 随着工艺进步,栅极长度物理尺寸的缩小已然没有规律可言, 但部分从业者(如三星、台积电)为了延续此前每隔一代大约能缩小0.7的规律,把后续的工艺制程,如当今的14nm,10nm,7nm制程,均是按照以上规律进行命名。 后续制程工艺命名和Gate Length物理尺寸已失去严格联系,业界又是如何判定不同厂商之间的工艺带差呢? 那便是芯片内部的 晶体管密度, 通过对比芯片内部的晶体管密度多少,即可判定是否属于先进工艺或是同一工艺。

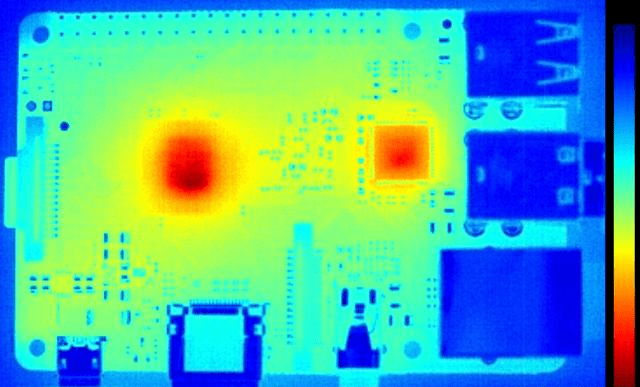

从表中可以看到,英特尔工艺在目前10nm节点上晶体管密度已经达到了已经达到了1.06亿/mm²,略超三星与台积电在7nm上分别0.95亿/mm²和0.97亿/mm²的密度。由此可以看出,Intel 10nm和同期台积电、三星等厂商工艺制程属于同一水平。 04 芯片晶体管的理论极限? 回忆一下晶体管的模型:一个晶体管由“源”“漏”两个电极组成,两个电极之间由沟道连接,由栅极开关控制。当开关打开时,沟道连接两个电极,电流可以流过;断开时,通道消失,电流无法通过。芯片技术越先进,晶体管沟道越短,电子通过沟道的时间越短,信息传输越快,芯片性能越好。 目前绝大多数沟道由硅基半导体制成,而一个硅原子的直径为0.2nm。如果沟道一直缩小到比原子直径还短,就意味 着源漏两个电极完全连接在一起,不再有通断区分,即晶体管失去开关功能,自然失效。 因此0.2nm也是沟道长度的理论极限。 但是,在沟道长度减小到0.2 nm之前,主要受另外两个物理定律的限制: 电流热效应与 量子隧穿。 晶体管工作时,电流通过沟道时受焦耳定律支配,会产生大量热。在目前的主流工艺下,晶体管大小仅仅有几十纳米甚至几纳米,晶体管密度不断上升,晶体管发热积少成多。当前高性能芯片,无论是手机处理器还是桌面乃至服务器处理器,其集成的晶体管数量从数亿到数十亿不等。同时由于CPU频率很高,比如i7处理器睿频能够达到3GHz以上。这就意味着,在性能峰值下,有相当数量的晶体管在每秒内翻转(0→1,1→0)次数高达3亿次。每次都伴随着电流消耗和热量的产生。由于散热速度远远小于其产生速度,于是就形成了如下图所示的局部高温区域,导致CPU运算时错误率上升,甚至导致宕机。

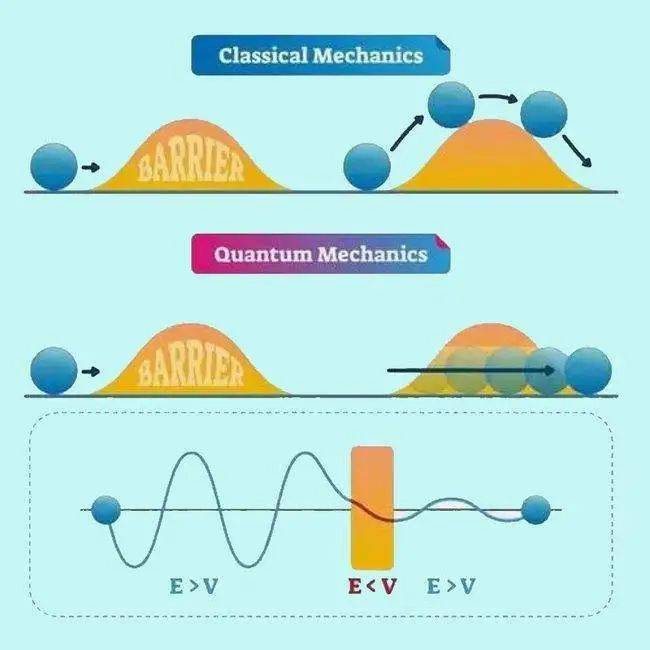

因此,晶体管尺寸进一步减少的进程受到发热的巨大挑战, 电流热效应的存在也直接导致了摩尔定律的失效。 另外,晶体管被 栅极关断时,源漏电极间沟道断开,在其尺寸较大的情况下,源漏电极间不会有电子交换。但当沟道缩小到非常短的尺寸时, 量子隧穿现象开始显现,电子可以如“穿墙”一样穿过沟道,到达另一个电极。此时,晶体管开关时源漏电极间均有电流通过,晶体管失去开关功能,因此失效。

结语 面临物理学极限,芯片制造工艺如何进一步突破?寻找可以代替硅基半导体的新型材料、寻找更优异的栅极材料与探求更优异的晶体管构造也许便是高端芯片的未来所在。这些问题,需要我们这些 材料学子去探寻答案。 ——END—— 参考文献: 材子风华 出品 I 金小象新媒体工作室 资料来源 I 材料学院青年双创服务中心 本期主编 I 米洋 责编 I 朱联璧荷 付誉 指导 I 李偲宸返回搜狐,查看更多 |

【本文地址】